| Name: | Solutions | (revised) | <br>Lecture Section: |

|-------|-----------|-----------|----------------------|

| ID#:  |           | _         |                      |

# DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

# ENEL 353 - Digital Circuits

## **Final Examination**

Lecture sections

**01**: N. R. Bartley, MWF 11:00–11:50 **02**: S. A. Norman, MWF 12:00–12:50

Monday, December 16, 2013 Time: Noon – 3:00 PM Location: Gold Gymnasium

### **Instructions:**

- Time allowed is 3 hours.

- Please review the examination rules on Page 2.

- Non-programmable calculators are permitted.

- The maximum number of marks is 100, as indicated. The final examination counts toward 50% of the final grade. Please attempt all questions.

- Please use a pen or heavy pencil to ensure legibility.

- Please answer questions in the spaces provided; if space is insufficient, please use the back of the pages.

- Where appropriate, marks will be awarded for proper and well-reasoned explanations.

|   | (Please do no |               |        |                 |        |        |        |                    |

|---|---------------|---------------|--------|-----------------|--------|--------|--------|--------------------|

| 1 | (14) 2 (14)   | <b>3</b> (13) | 4 (12) | 5 <i>(11)</i> 6 | 6 (10) | 7 (12) | 8 (14) | <b>Total</b> (100) |

|   |               |               |        |                 |        |        |        | Y                  |

|   | · ·           |               |        |                 |        |        |        |                    |

#### Student Identification

Each candidate must sign the Seating List confirming presence at the examination. All candidates for final examinations are required to place their University of Calgary I.D. cards on their desks for the duration of the examination. (Students writing mid-term tests can also be asked to provide identity proof.) Students without an I.D. card who can produce an **acceptable** alternative I.D., e.g., one with a printed name and photograph, are allowed to write the examination.

A student without acceptable I.D. will be required to complete an Identification Form. The form indicates that there is no guarantee that the examination paper will be graded if any discrepancies in identification are discovered after verification with the student's file. A student who refuses to produce identification or who refuses to complete and sign the Identification Form is not permitted to write the examination.

#### **Examination Rules**

- (1) Students late in arriving will not normally be admitted after one-half hour of the examination time has passed.

- (2) No candidate will be permitted to leave the examination room until one-half hour has elapsed after the opening of the examination, nor during the last 15 minutes of the examination. All candidates remaining during the last 15 minutes of the examination period must remain at their desks until their papers have been collected by an invigilator.

- (3) All inquiries and requests must be addressed to supervisors only.

- (4) The following is strictly prohibited:

- (a) speaking to other candidates or communicating with them under any circumstances whatsoever;

- (b) bringing into the examination room any textbook, notebook or document not authorized by the examiner;

- (c) making use of calculators, cameras, cell-phones, computers, headsets, pagers, PDA's, or any device not authorized by the examiner;

- (d) leaving examination papers exposed to view;

- (e) attempting to read other student's examination papers.

The penalty for violation of these rules is suspension or expulsion or such other penalty as may be determined.

- (5) Candidates are requested to write on both sides of the page, unless the examiner has asked that the left hand page be reserved for rough drafts or calculations.

- (6) Discarded matter is to be struck out and not removed by mutilation of the examination answer book.

- (7) Candidates are cautioned against writing on their examination paper any matter extraneous to the actual answering of the question set.

- (8) The candidate is to write his/her name on each answer book as directed and is to number each book.

- (9) During the examination a candidate must report to a supervisor before leaving the examination room.

- (10) Candidates must stop writing when the signal is given. Answer books must be handed to the supervisor-in-charge promptly. Failure to comply with this regulation will be cause for rejection of an answer paper.

- (11) If during the course of an examination a student becomes ill or receives word of a domestic affliction, the student should report at once to the supervisor, hand in the unfinished paper and request that it be cancelled. If physical and/or emotional ill health is the cause, the student must report at once to a physican/counsellor so that subsequent application for a deferred examination is supported by a completed Physician/Counsellor Statement form. Students can consult professionals at University Health Services or Counselling and Student Development Centre during normal working hours or consult their physician/counsellor in the community. Once an examination has been handed in for marking a student cannot request that the examination be cancelled for whatever reason. Such a request will be denied. Retroactive withdrawals will also not be considered.

- 1. [14 marks total.] Numbers, codes and binary addition.

- (a) [1 mark.] Interpreted as an unsigned binary integer, what decimal number does 1000101 represent?

Unsigned:

$$2^6 + 2^2 + 2^9 = 64 + 4 + 1 = 69_{10}$$

(b) [1 mark.] Interpreted as a sign/magnitude integer, what decimal number does 1000101 represent?

Sign = 1 (negative), magnitude =

$$000101$$

, number is  $-5_{10}$

(c) [2 marks.] Interpreted as a two's complement integer, what decimal number does 1000101 represent?

Negative number. Determine its magnitude

Number is

$$-(2^5 + 2^4 + 2^3 + 2^3 + 2^3 + 2^5) = -59_{10}$$

(d) [3 marks.] Convert the octal number 65728 to each of the formats given below. Show how you obtained your answers.

hexadecimal: Regroup bits decimal:

$$6 \times 8^3 + 5 \times 8^2 + 7 \times 8^1 + 2 \times 8^0$$

$$\frac{110 \text{ for 11} 1010}{20 + 101} = 207R_{10}$$

- (e) [1 mark.] The ten-bit Gray code for  $353_{10}$  is 0111010001. Explain briefly but precisely why it cannot possibly be true that 0111010100 is the ten-bit Gray code for 35410. Gray code ensures that an increase by 1 in the binary code causes only 1 bit to change in the Gray code. 2 bits change here.

- (f) [2 marks.] An example 8-bit adder is shown to the right. Recall that signed overflow is a condition that may occur when using an N-bit adder to add two'scomplement integers.

Write an SOP expression involving bits of a, b, and s that is true if and only if signed overflow has occurred, and write a one-sentence explanation of why your expression is correct. (Do not include carry signals in your

expression.)  $V = a_7b_7\overline{5}_7 + \overline{a}_7\overline{b}_7\overline{5}_7$  sign bit  $a_7, b_7, s_7$ This will be true if adding two numbers of the same sign produces a sum with the opposite sign.

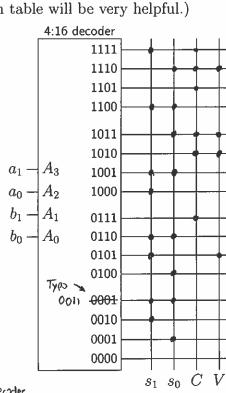

(g) [4 marks.] Consider building a 2-bit integer adder, with  $a_1 - a_1 - a_1 - a_1$ inputs and outputs as shown to the right.  $s_{1:0}$  is the 2bit sum of  $a_{1:0}$  and  $b_{1:0}$ , C is true to indicate unsigned overflow, and V is true to indicate signed overflow.

| -        | $a_1$ | $s_1$ | _        |

|----------|-------|-------|----------|

| -        | $a_0$ | $s_0$ | H        |

| -        | $b_1$ | C     | $\vdash$ |

| $\dashv$ | $b_0$ | V     | _        |

Use dot notation on the given ROM circuit to show how to implement the adder as a ROM. (Hint: The given truth table will be very helpful.)

| $a_1$ | $a_0$ | $b_1$ | $b_0$ | Cout | $s_1$ | $s_0$ | С | ٧ |

|-------|-------|-------|-------|------|-------|-------|---|---|

| 0     | 0     | 0     | 0     | 0    | 0     | 0     | ٥ | 0 |

| 0     | 0     | 0     | 1     | 0    | 0     | 1     | 0 | C |

| 0     | 0     | 1     | 0     | 0    | 1     | 0     | 0 | Ö |

| 0     | 0     | 1     | 1     | 0    | 1     | 1     | 0 | 0 |

| 0     | 1     | 0     | 0     | 0    | 0     | 1     | О | 0 |

| 0     | 1     | 0     | 1     | 0    | 1     | 0     | 0 | - |

| 0     | 1     | 1     | 0     | 0    | 1     | 1     | ٥ | 0 |

| 0     | 1     | 1     | 1     | 1    | 0     | 0     | 1 | 0 |

| 1     | 0     | 0     | 0     | 0    | 1     | 0     | O | 0 |

| 1     | 0     | 0     | 1     | 0    | 1     | 1     | 0 | 0 |

| 1     | 0     | 1     | 0     | 1    | 0     | 0     | 1 | 1 |

| 1     | 0     | 1     | 1     | 1    | 0     | 1     | 1 | 1 |

| 1     | 1     | 0     | 0     | 0    | 1     | 1     | ø | 0 |

| 1     | 1     | 0     | 1     | 1    | 0     | 0     | 1 | 0 |

| 1     | 1     | 1     | 0     | 1    | 0     | 1     | 1 | 1 |

| 1     | 1     | 1     | 1_    | 1    | 1     | 0     | 1 | O |

Note reverse order of input combinations between table and decoder.

- 2. [14 marks total.] Boolean algebra and multiplexers.

- (a) [2 marks.] The XOR operator has a number of its own important basic properties. In the table below, determine the result of each XOR operation.

| Operation          | Result |

|--------------------|--------|

| $A \oplus A$       | 0      |

| $A \oplus 1$       | Ā      |

| $A \oplus \bar{B}$ | A 🕀 B  |

$$A \oplus A = R \overline{A} + \overline{A} A = 0$$

$$A \oplus 1 = A \cdot 0 + \overline{A} \cdot 1 > \overline{A}$$

$$A \oplus \overline{B} = AB + \overline{A}B = \overline{A \oplus B}$$

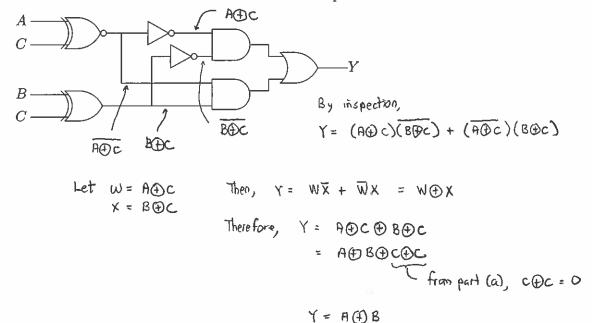

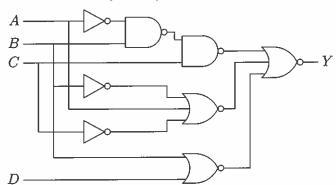

(b) [5 marks.] In the circuit shown below, algebraically prove or disprove that  $Y = A \oplus B$ . Do not use a truth table or K-map.

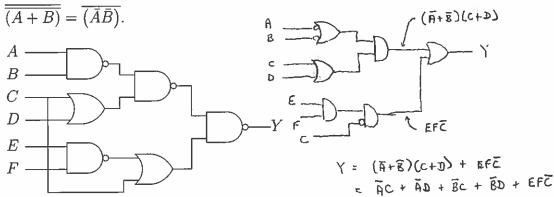

(c) [3 marks.] Use bubble-pushing and/or algebra to find a SOP expression for Y. If you use bubble-pushing, draw your equivalent circuit to the right of the given circuit. Hint for bubble-pushing with OR gates: A+B=

(d) [4 marks.] Draw a schematic to show how the function  $Y = AB + \bar{B}C + A\bar{C}$  can be implemented with a 2:1 multiplexer, one inverter, and one two-input AND gate.

- 3. [13 marks total.] K-map and multiple-output problems.

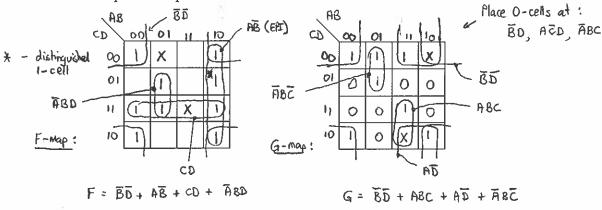

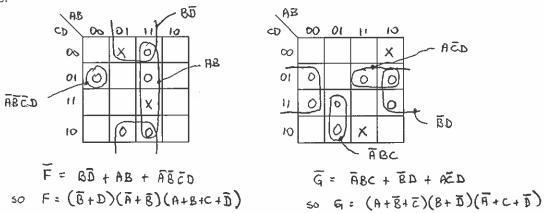

- (a) [6 marks.] Consider the following two logic functions with the given don't-care conditions:

| Function   | Expression                                                       | Don't-cares                 |

|------------|------------------------------------------------------------------|-----------------------------|

| F(A,B,C,D) | $\bar{B}\bar{C}\bar{D} + A\bar{B} + \bar{A}\bar{B}C + \bar{A}BD$ | $ar{A}Bar{C}ar{D},ABCD$     |

| G(A,B,C,D) | $(B+\bar{D})(\bar{A}+C+\bar{D})(A+\bar{B}+\bar{C})$              | $Aar{B}ar{C}ar{D},ABCar{D}$ |

Use the blank K-maps below to determine minimal SOP expressions for each of F and G:

- i. If there is more than one solution for either, give just one, but indicate how many other solutions are possible;

- ii. On the map for F, indicate all of the distinguished 1-cells and the essential prime implicants.

There are two other possible solutions

There is one other possible solution

(b) [4 marks.] Use the same maps from part (a) to determine minimal POS expressions for each of F and G. If there are multiple solutions, give just one.

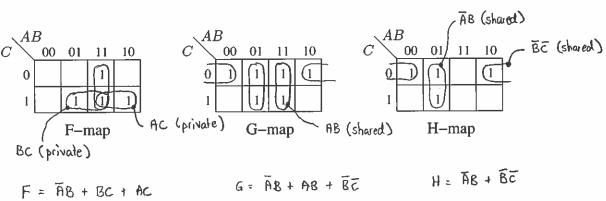

(c) [3 marks.] The K-maps below describe a system with three inputs and three outputs. Write equations for F, G, and H suitable for implementation on a PLA using the *smallest number of implicants*. Do not draw a PLA diagram.

There are a total of 5 implicants used (3 shared, 2 private).

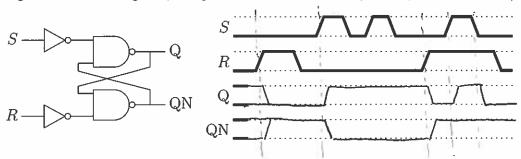

- 4. [12 marks total.] Questions about basic building blocks for sequential circuits.

- (a) [3 marks.] An SR latch can be made from two NOT gates and two NAND gates, as shown below. Complete the timing diagram. (Note that for the given S and R signals, it's possible to determine Q and QN at all times.)

Remark: When S=R=1, both NAND gates have a 0 input, so Q=QN=1.

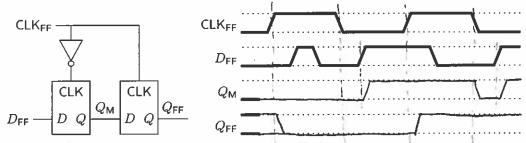

(b) [3 marks.] The schematic below shows a D flip-flop made from two D latches in a master-slave configuration. Complete the timing diagram.

Remark: Because of the NOT gate, an follows DFF when CLKFF is LOW.

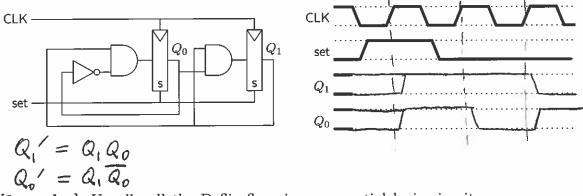

(c) [3 marks.] The set inputs to the DFFs in this circuit are synchronous. Complete the timing diagram.

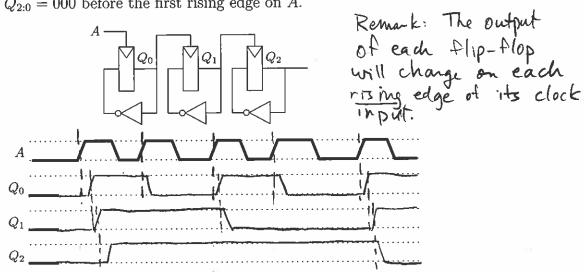

(d) [3 marks.] Usually all the D flip-flops in a sequential logic circuit are connected to the same clock source. However, it's possible to create some interesting and useful circuits by breaking that rule.

Complete the timing diagram for the given circuit. Assume that the pulses on A are much wider than any of the DFF timing parameters, and that  $Q_{2:0} = 000$  before the first rising edge on A.

- 5. [11 marks total.] Constraints related to voltage levels and timing.

- (a) [3 marks.] The table below on the left specifies important voltage levels for Advanced Ultra-Low Voltage CMOS operating with  $V_{\rm DD}=1.8\,\rm V$ . Fill in the table on the right with either the most precise possible range of output voltages, or an explanation of why the range is unknown.

|                                                                                                                                   | gate                                       | output range or explanation                                 | Remarks                      |

|-----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------------------------------------------------------------|------------------------------|

| $V_{\mathrm{OH}}$ 1.20 V                                                                                                          | 1.18 V ———                                 | 0 = Vout = 0.45 ¥                                           | Vm Z VIH                     |

| $egin{array}{c c} V_{ m IH} & 1.17{ m V} \\ \hline V_{ m IL} & 0.63{ m V} \\ \hline V_{ m OL} & 0.45{ m V} \\ \hline \end{array}$ | 0.05 V<br>0.50 V<br>1.05 V                 | Unknown. Two mputs eve<br>OK, but 1-05V 13 n forbidden zone | ,                            |

| VOL 0.40 V                                                                                                                        | 0.52 V ——————————————————————————————————— | 1.20V = Vout = 1.8V                                         | 0.52 Y ≤ VIL<br>1.70 V ≥ VIH |

(b) [3 marks.] Determine overall  $t_{\rm pd}$  and  $t_{\rm cd}$  values for the following circuit. Show carefully how you obtained your answers.

Timing parameters in ps

| gate | # inputs | $\mathbf{t_{pd}}$ | $\mathbf{t_{cd}}$ |

|------|----------|-------------------|-------------------|

| NOT  | 1        | 30                | 21                |

| NAND | 2        | 43                | 32                |

| NAND | 3        | 53                | 42                |

| NOR  | 2        | 55                | 40                |

| NOR  | 3        | 70                | 54                |

Overall topd =

$$\frac{30}{N07}$$

+  $\frac{43}{N002}$  +  $\frac{70}{N002}$  =  $\frac{186}{P5}$  Overall tod =  $\frac{32}{N002}$  +  $\frac{54}{N002}$  =  $\frac{86}{P5}$

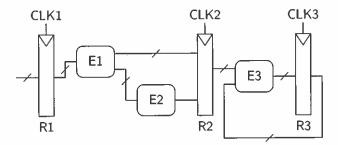

(c) [2 marks.] In the following circuit, signals CLK1, CLK2, and CLK3 all come from the same clock source. For all three registers, the timing parameters are  $\mathbf{t}_{\text{setup}} = 50 \, \text{ps}$ ,  $\mathbf{t}_{\text{hold}} = 0 \, \text{ps}$ ,  $\mathbf{t}_{\text{pcq}} = 40 \, \text{ps}$ , and  $\mathbf{t}_{\text{ccq}} = 25 \, \text{ps}$ .

Timing parameters in ps

| element | $\mathbf{t_{pd}}$ | $\mathbf{t_{cd}}$ |

|---------|-------------------|-------------------|

| E1      | 100               | 41                |

| E2      | 200               | 55                |

| E3      | 280               | 70                |

Assume the input to R1 never violates timing constraints, and that there is zero clock skew between CLK1, CLK2, and CLK3. Determine the minimum  $T_{\rm C}$  (clock period) for reliable operation of the circuit.

The critical palm 13 from R1 to R2 thru E1 and E2.

$$tpd = 100 + 200 = 300ps$$

.

$T_c \le tpcq + tpd + tsetup = 40 + 300 + 50 = 390ps$

(d) [3 marks.] Consider again the circuit of part (c), but now assume that there might be some clock skew. Suppose the desired  $T_{\rm C}$  is 460 ps. What is the maximum value of  $t_{\rm skew}$  that will allow reliable operation?

is the maximum value of t<sub>skew</sub> that will allow reliable operation?

Setup From (c), tpd = 300ps | hold Overall tcd is 41ps (RI to RZ thru EI)

tskew = Tc - tpcq - tpd - tsetup | tcd = thold - tccq + tskew

\[

\leq 460 - 40 - 300 - 50 | tskew \leq tcd - thold + tccq = 41 - 0 + 25

\]

tskew \leq 70ps

Overall: \[

\text{tskew} \leq 66ps

\]

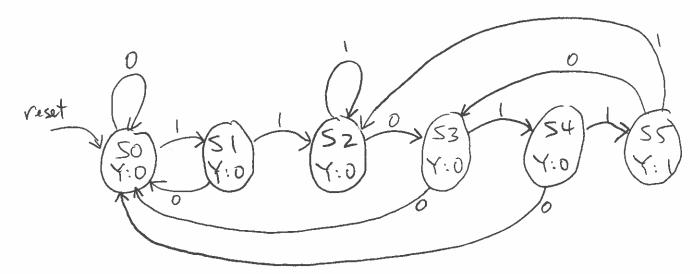

- 6. [10 marks total.] A sequence detection problem. Consider the design of a Moore-type FSM that has one input A and one output Y. Y should be 1 if the values of A at the last 5 rising edges of the clock have been 1, 1, 0, 1, 1. Y should be 0 at all other times.

- (a) [7 marks.] Choose states for an FSM design, and describe them in the table below. (If you need fewer than eight states, write "unused" beside the names of states you don't use.) Then make a state-transition diagram for the FSM.

| state | description                                 |

|-------|---------------------------------------------|

| S0    | from reset, or looking for first 1 in 11011 |

| S1    | looking for second 1 in 11011               |

| S2    | looking for 0 within 11011                  |

| S3    | looking for third I m 11011                 |

| S4    | looking for fourth 1 in 11011               |

| S5    | sequence detected ove last 5 vising edges   |

| S6    | unused                                      |

| S7    | unused                                      |

Remark: The direct path from 50 to 55 is easy. The harden part is determining how far to "back up" when an "undesired bit" arrives.

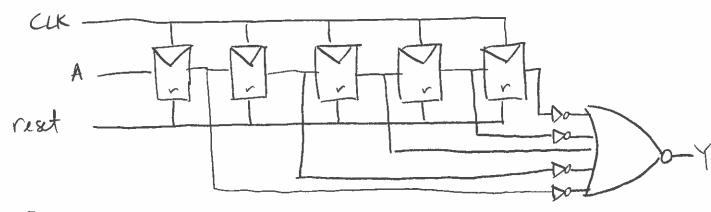

(b) [3 marks.] Instead of going on to make tables for next-state and output logic, consider a totally different method of implementation. Draw a schematic for the sequence detector, using 5 D flip-flops in a shift register configuration, one NOR gate with however many inputs you need, and some inverters.

Remark: Remember that DeMorgan's Theorem lets you convert a NOR gate into an AND gate.

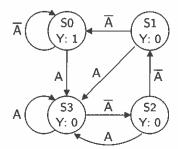

- 7. [12 marks total.] FSM implementation in a "programmable FSM" circuit.

- (a) [4 marks.] Below are a state transition diagram of an FSM and a proposed state encoding. Write truth tables for the next-state and output logic.

| state | $S_1$ | $S_0$ |

|-------|-------|-------|

| S0    | 0     | 0     |

| S1    | 0     | 1     |

| S2    | 1     | 0     |

| S3    | 1     | 1     |

| next-state logic |    |              |      |     |  |  |

|------------------|----|--------------|------|-----|--|--|

| 5,               | 50 | A            | 15,1 | So' |  |  |

| 0                | 0  | 0            | 0    | 0   |  |  |

| 0                | 0  | 1            | 11   | ĺ   |  |  |

| 0                | (  | 0            | 0    | 0   |  |  |

|                  |    |              | 1    |     |  |  |

| -                | 0  | Q            | 0    | l l |  |  |

| 1                | 0  | - {          | 11   | 1   |  |  |

| 1                | 1  | 0            | l    | 0   |  |  |

| 1                |    | <b>(</b> *** | 1 (  | 1   |  |  |

| out | out_           | 10912 |

|-----|----------------|-------|

| 7   | S <sub>0</sub> | Y     |

| 1   | 0              | 000   |

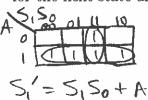

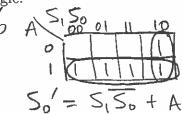

(b) [3 marks.] Use the results of part (a) to find minimal SOP expressions for the next-state and output logic.

5,1

By respection

$$Y = \overline{5}, \overline{5}_0$$

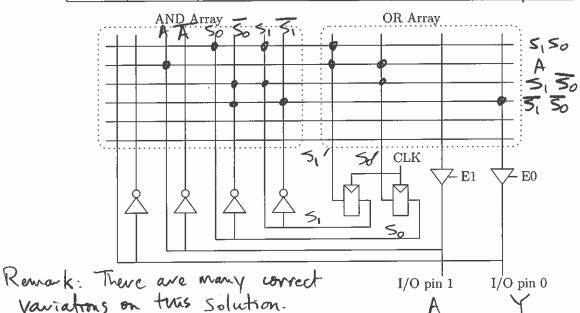

(c) [5 marks.] The FSM can be implemented using a "programmable FSM", which combines a PLA, some D flip-flops, and some tristate buffers, as shown below. A decision has been made to use I/O pin 1 for A and I/O pin 0 for Y.

Fill in the table to specify and explain the correct values for E1 and E0, then put dots in the AND and OR Arrays in the PLA to implement your equations from part (b).

| signal | 0 or 1? | reason                                   |

|--------|---------|------------------------------------------|

| E1     | 0       | A must not contend with OR array output. |

| E0     | l       | I must be driven by OR array output.     |

- 8. [14 marks total.] Questions about FSM analysis.

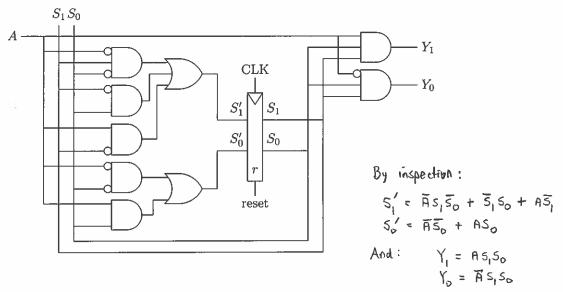

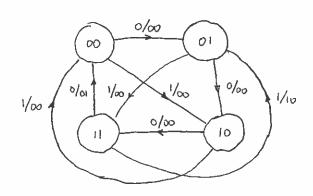

- (a) [8 marks.] Consider the FSM sketched below. There is one input A, and two outputs  $Y_1$  and  $Y_0$ . Determine the combined state and output table, and sketch the state-transition diagram. In your tables, use 0's and 1's for the states and next states, not symbols like S0, S1, etc.

Combined state and output table:

| Current state | input<br>A | next-state<br>siso' | tuqtuo<br>ov ,Y |

|---------------|------------|---------------------|-----------------|

| 00            | 0          | 0                   | 0 0             |

| 00            | t          | 0 1                 | 00              |

| 01            | 0          | 10                  | 00              |

| 01            | 1          | 1 1                 | 00              |

| 10            | 0          | 11                  | 00              |

| 10            | 1          | 0 0                 | 00              |

| ° (1          | 0          | 0 0                 | 0 +             |

| t I           |            | 0 1                 | 10              |

State-transition diagram:

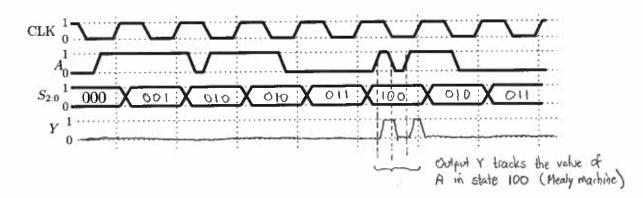

(b) [6 marks.] Below is the combined state and output table for a FSM that has one input A, and one output Y. The state variables are S<sub>2:0</sub>. Use this table to complete the timing diagram.

| $S_{2:0}$ | A | $S'_{2:0}$ | Y | $S_{2:0}$ | A | $S'_{2:0}$ | Y |

|-----------|---|------------|---|-----------|---|------------|---|

| 000       | 0 | 000        | 0 | 010       | 1 | 010        | 0 |

| 000       | 1 | 001        | 0 | 011       | 0 | 100        | 0 |

| 001       | 0 | 000        | 0 | 011       | 1 | 001        | 0 |

| 001       | 1 | 010        | 0 | 100       | 0 | 000        | 0 |

| 010       | 0 | 011        | 0 | 100       | 1 | 010        | 1 |